## 緒電晶體負偏壓不穩定性 之臨界電壓方法論

系所/電子工程學系 指導老師/邱福千

組員/吳俊葳、周蘋歆、林子馨、魏廷翔

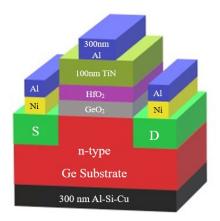

隨著互補式金屬氧化物半導體 (CMOS)的微縮,具有高電洞遷移率的 P 型鍺金屬氧化物半導體場效應電 晶體 (Ge-pMOSFET),被認為是下一個技術節點很可能使用的材料。在這裡提出了 Al/TiN/HfO2/GeO2 閘極堆疊(Gate stack)鍺金屬氧化物半導體場效應電晶體,閘極堆疊降低了鍺元件的等效氧化層厚度(EOT),但仍有不可忽視的可靠度問題,我們對鍺元件的時依性介電層崩潰(Time Dependent Dielectric Breakdown, TDDB) 和負偏壓溫度不穩定性效應(Negative Bias Temperature Instability, NBTI)進行可靠度分析。

在 NBTI 部分,我們由冪律模型 (Power Law Model)預測元件經過十年後可正常操作的閘極電壓,並且發現本體陷阱(bulk trap)主導 NBTI 且可以恢復(recovery)。

在 TDDB 部分,我們以  $\ln(-\ln(1-f))$ 對  $\ln(x/\alpha)$ 作圖,所得到的斜率即是韋布斜率( $\beta$ ),可用來判斷其可靠度。

最後,我們分析閘極氧化層的電

荷捕獲(charge trapping)所造成的漏電流,並得到經由應力而產生的陷阱之行為、產生時隨時間的相依性等等, 得出了此材料當介電質時產生之陷阱的特性。

圖 1:Ge p-MOSFETs

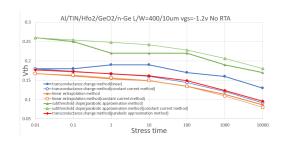

下圖(圖 2)使用二次微分法、拋物 線法、外插法、次臨界擺幅、與各個方 法之定電流,取得在各個 stress time 之 下的臨界電壓。

圖 2: Stress time-Vth